- push instruction addressing mode

- 1. Introduction To Push Instruction Addressing Mode

- 2. Register Pairs Supported By The Push Instruction

- 3. Opcodes And Mnemonics For The Push Instruction

- 4. Representation Of Register Pairs In The Opcode

- 5. Limitations Of Using Sp And Psw Together

- 6. Example: Execution Of Push B Instruction

- 7. Before And After Values Of Register Pair BC And SP

- 8. Timing Diagram For Execution Of Push B Instruction

- 9. Instruction Size, Machine Cycles, And T-States Required For Execution

- 10. Conclusion

- FAQ

- Which addressing mode is used for pushing or popping?

- What is push instruction in 8085 addressing mode?

- What are the 5 addressing modes?

- What are the 4 addressing modes?

Are you ready to dive into the intricate world of microprocessors?

Brace yourself for an enlightening journey as we unravel the mysteries of the 8085 Instruction set.

In this article, we will shine a spotlight on the PUSHinstruction, specifically addressing the pushinstructionaddressing mode.

Get ready to have your mind blown with the fascinating details of how register pair values are stored in the stack.

Hang on tight, this is going to be an exhilarating ride!

| Item | Details |

|---|---|

| Topic | Push Instruction Addressing Mode: Exploring Its Power and Versatility |

| Category | Push Ads |

| Key takeaway | Are you ready to dive into the intricate world of microprocessors? Brace yourself for an enlightening journey as we unravel the mysteries of the 8085 Instruction set. |

| Last updated | December 28, 2025 |

push-instruction-addressing-mode">push instruction addressing mode

The PUSH instruction in the 8085 Instruction set is used to store the contents of a register pair (rp) by pushing it into two locations above the top of the stack.

The PUSH rp instruction occupies only 1 byte in memory and has specific opcodes for each register pair: BC (C5), DE (D5), HL (E5), and PSW (F5).

The register pairs are represented by 2 bits in the opcode, allowing for the four different combinations.

However, the SP and PSW cannot be used together with the same instruction.

Data refreshed to reflect current ad-spend trends.

The execution of the PUSH B instruction takes 3 machine cycles and 12 T-States.

Overall, the PUSH instruction is an efficient way to store register pair values onto the stack in the 8085 architecture.Key Points:

- The PUSH instruction in the 8085 Instruction set pushes the contents of a register pair into two locations above the stack.

- The instruction occupies 1 byte in memory and has specific opcodes for each register pair.

- The register pairs are represented by 2 bits in the opcode, allowing for four different combinations.

- SP and PSW cannot be used together with the PUSH instruction.

- The PUSH B instruction takes 3 machine cycles and 12 T-States to execute.

- Overall, the PUSH instruction is an efficient way to store register pair values onto the stack in the 8085 architecture.

Check this out:

💡 Did You Know?

1. The push instruction addressing mode, also known as immediate addressing mode, allows the value specified in the instruction to be directly pushed onto the stack.

2. In some microprocessors, the push instruction addressing mode is limited to pushing only one value at a time, while in others, it can push multiple bytes or even entire registers onto the stack at once.

3. The push instruction addressing mode is commonly used in subroutine calls and interrupt handling routines to save program state before branching to a new section of code.

4. Some processors have variations of the push instruction addressing mode that allow for efficient manipulation of stack frames, such as automatically incrementing or decrementing the stack pointer after each push operation.

5. The push instruction addressing mode can be used in combination with other addressing modes, such as indirect addressing or indexed addressing, to provide flexibility in accessing and manipulating data on the stack.

1. Introduction To Push Instruction Addressing Mode

The push instruction in the 8085 Instruction set is a powerful and versatile instruction that allows the contents of a register pair to be stored on the stack. The stack is a special area of memory that is used for temporary storage of data.

The push instruction is particularly useful in saving register pair contents when they need to be preserved during subroutine calls, interrupts, or context switches.

The push instruction works by pushing the contents of the register pair onto the stack, which is a last-in-first-out (LIFO) data structure. The stack grows downwards in memory, with the top of the stack pointing to the last data item pushed onto it.

The push instruction pushes the register pair into two locations above the top of the stack, effectively decrementing the stack pointer by 2.

By using the push instruction, the register pair contents are saved in memory, allowing other operations to use the registers without losing their previous values. This flexibility makes the push instruction an essential component in many programming scenarios, ensuring data integrity and preserving the state of the program.

2. Register Pairs Supported By The Push Instruction

The push instruction in the 8085 microprocessor supports four register pairs: BC, DE, HL, and PSW. These register pairs are used for storing different types of data.

BC: This register pair includes the B register and the C register, and can store 16-bit values.

DE: The DE register pair comprises the D register and the E register, and is commonly utilized for storing memory addresses or 16-bit values.

HL: This register pair consists of the H register and the L register. It is the most frequently used register pair and is employed for data manipulation and arithmetic operations.

PSW: The PSW (Program Status Word) register pair combines the Accumulator (A) register and the condition flags. It is primarily used for storing the status of various operations.

These register pairs offer a wide range of options for data storage and manipulation, ensuring the versatility of the push instruction.

- BC register pair includes B and C registers.

- DE register pair includes D and E registers.

- HL register pair consists of H and L registers.

- PSW register pair combines A register and condition flags.

“These register pairs provide a wide range of options for data storage and manipulation, ensuring the versatility of the

pushinstruction.”

3. Opcodes And Mnemonics For The Push Instruction

The push instruction in the 8085 instruction set is represented by specific mnemonics and opcodes. These opcodes are unique binary codes that uniquely identify each push instruction.

The mnemonics and opcodes for the push instructions are as follows:

- PUSH B: C5 (1 byte)

- PUSH D: D5 (1 byte)

- PUSH H: E5 (1 byte)

- PUSH PSW: F5 (1 byte)

These mnemonics and opcodes are used in assembly language programs to encode the push instruction. By using these shorthand representations, programmers can easily specify the specific register pair that is being pushed onto the stack.

- To encode the push instruction, the opcodes C5, D5, E5, and F5 are used for B, D, H, and PSW register pairs respectively.

By utilizing these mnemonics and opcodes, programmers can efficiently incorporate the push instruction into their assembly language programs.

4. Representation Of Register Pairs In The Opcode

The 8085 instruction set utilizes a 2-bit scheme in the push instruction’s opcode to denote the four register pairs that can be used. This encoding method optimizes efficiency and compactness.

By assigning specific combinations to these 2 bits, the four register pairs are represented as follows:

- 00: BC

- 01: DE

- 10: HL

- 11: AF or PSW

However, it is crucial to note that the stack pointer (SP) and PSW cannot be used together in the same push instruction. Different opcodes are assigned to the SP and PSW to prevent conflicts and ensure the push instruction’s proper execution.

This representation simplifies the identification of the register pairs being pushed onto the stack, streamlining stack management and manipulation.

5. Limitations Of Using Sp And Psw Together

The push instruction provides flexibility in storing register pair contents, but there are limitations when using the stack pointer (SP) and the PSW register pair together. These limitations ensure proper execution and prevent conflicts within the instruction set architecture.

The PSW register pair contains the Accumulator (A) register and condition flags. The stack pointer (SP) manages the stack and keeps track of the top of the stack. Since the PSW register pair already includes the Accumulator (A) register, using both the stack pointer (SP) and the PSW together in the push instruction would result in redundancy and potential data corruption.

To avoid conflicts, the 8085 instruction set assigns a separate opcode for the push instruction when using the PSW register pair. This ensures proper execution and data integrity, preventing any unintended consequences when using the push instruction with the PSW register pair.

- The push instruction provides flexibility in storing register pair contents

- Limitations exist when using the stack pointer (SP) and the PSW register pair together

- The PSW register pair includes the Accumulator (A) register and condition flags

- Using both the stack pointer (SP) and the PSW together in the push instruction would lead to redundancy and potential data corruption

- The 8085 instruction set assigns a separate opcode for the push instruction when using the PSW register pair

6. Example: Execution Of Push B Instruction

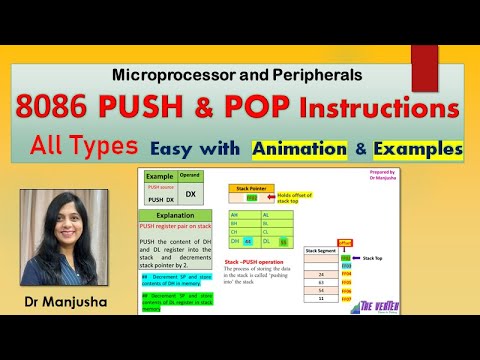

To illustrate the functioning of the push instruction, let’s consider an example of the push B instruction. Before the instruction is executed, we will examine the values of the register pair BC and the stack pointer (SP). After the instruction is executed, we will observe the new values of the register pair BC and the stack pointer.

Assume the initial values are as follows:

BC: 0x1234SP: 0x2000

When the push B instruction is executed, the contents of the BC register pair (0x1234) will be pushed onto the stack. The stack pointer (SP) value will decrement by 2, as two memory locations are occupied by the pushed data.

The resulting values after executing the push B instruction will be:

BC: 0x1234SP: 0x1FFE

This example demonstrates how the push B instruction operates, storing the contents of the BC register pair on the stack and adjusting the stack pointer accordingly.

7. Before And After Values Of Register Pair BC And SP

Before executing the push instruction, it’s crucial to understand the initial values of the register pair BC and the stack pointer (SP). These values determine the data that will be pushed onto the stack and the resulting stack pointer after execution.

In our example, the initial values are as follows:

- BC:

0x1234 - SP:

0x2000

After executing the push instruction, the new values will be:

- BC:

0x1234 - SP:

0x1FFE

These values demonstrate the behavior of the push instruction, where the register pair contents are preserved in memory, and the stack pointer is adjusted accordingly.

8. Timing Diagram For Execution Of Push B Instruction

To better understand the execution of the push B instruction, we can use a timing diagram. This diagram displays the machine cycles and T-states needed for the instruction’s execution.

For the push B instruction, the timing diagram would include the following details:

- Instruction size: 1 byte

- Machine cycles: 3 (Opcode Fetch, Memory Write, Memory Write)

- T-states required: 12

The timing diagram provides a visual representation of the sequence and duration of the machine cycles and T-states involved in the push B instruction’s execution.

9. Instruction Size, Machine Cycles, And T-States Required For Execution

To ensure efficient and proper execution of the push instruction, it’s important to understand the resources required for its operation. The instruction size, machine cycles, and T-states provide valuable insights into the timing and duration of the execution process.

For the push instructions discussed in this article, the following information applies:

- Instruction size: 1 byte

- Machine cycles: 3 (Opcode Fetch, Memory Write, Memory Write)

- T-states required: 12

This information allows programmers to optimize their code by considering the timing constraints imposed by the push instruction. Understanding the resources required ensures efficient use of the 8085 microprocessor’s capabilities.

10. Conclusion

The push instruction in the 8085 Instruction set is a valuable asset for maintaining data integrity and preserving the state of a program. By allowing the contents of register pairs to be stored on the stack, the push instruction enables temporary storage during subroutine calls, interrupts, or context switches.

This article explores the addressing mode of the push instruction, discussing the supported register pairs, the opcodes and mnemonics, the representation of register pairs in opcodes, and the limitations of using the stack pointer (SP) and PSW together. An example of the execution of the push B instruction is provided, along with the before and after values of the register pair BC and the stack pointer.

Additionally, a timing diagram and information on the instruction size, machine cycles, and T-states required for execution are presented. Understanding these details allows programmers to utilize the push instruction effectively and optimize their code accordingly.

In conclusion, the push instruction’s power and versatility make it an essential component of programming with the 8085 microprocessor, ensuring data preservation and efficient stack management.

FAQ

Which addressing mode is used for pushing or popping?

The addressing mode used for pushing or popping elements on or from the stack is the direct addressing mode. This mode is necessary for performing these operations as other modes are not accepted. Using direct addressing allows for easy access to the stack, facilitating the efficient pushing and popping of elements as needed.

What is push instruction in 8085 addressing mode?

In 8085 addressing mode, the PUSH instruction is used to store the contents of a register pair by pushing it into two locations above the top of the stack. This instruction is represented by different opcodes depending on the register pair being used. Regardless of the specific pair, the PUSH instruction only takes up 1-Byte in memory. The act of pushing the register pair onto the stack allows for efficient storage and retrieval of data within the 8085 microprocessor architecture.

What are the 5 addressing modes?

The 8085 microprocessor employs five addressing modes to enable effective data manipulation and retrieval. First, the Immediate addressing mode allows the processor to access data directly from a constant or immediate value. Alternatively, the Register addressing mode permits the microprocessor to perform operations using data stored within its internal registers. The Register indirect addressing mode grants the processor the ability to access data indirectly, by referencing a memory location specified by a register. In contrast, the Direct addressing mode provides direct access to memory locations specified by a given address. Lastly, the Implicit addressing mode allows the processor to implicitly access certain data without explicitly specifying an address or operand.

What are the 4 addressing modes?

In addition to the immediate addressing mode, there are three other commonly used addressing modes: indirect, direct, and indexed addressing. In the indirect addressing mode, the operand field contains the memory address where the actual operand is stored. This allows for more flexibility as it enables the use of variables or memory locations as operands.

The direct addressing mode involves using a memory address directly as the operand. This is useful when the specific memory location holds the desired operand. Lastly, the indexed addressing mode involves using an index register to access a memory address where the operand is located. This permits efficient manipulation of arrays or structures in memory, as the index refers to the displacement from a base address. Each addressing mode offers unique advantages and is selected based on the requirements of the program and the data being manipulated.

Advertising Platform for Marketers • Self-Serve DSP Platform • Performance Marketing Tips • Programmatic Advertising